Menu, choosing Display and setting Display Levels from 0 toģ2) To switch back, hit CTRL-F, or set the Display Levels back to 0 from the

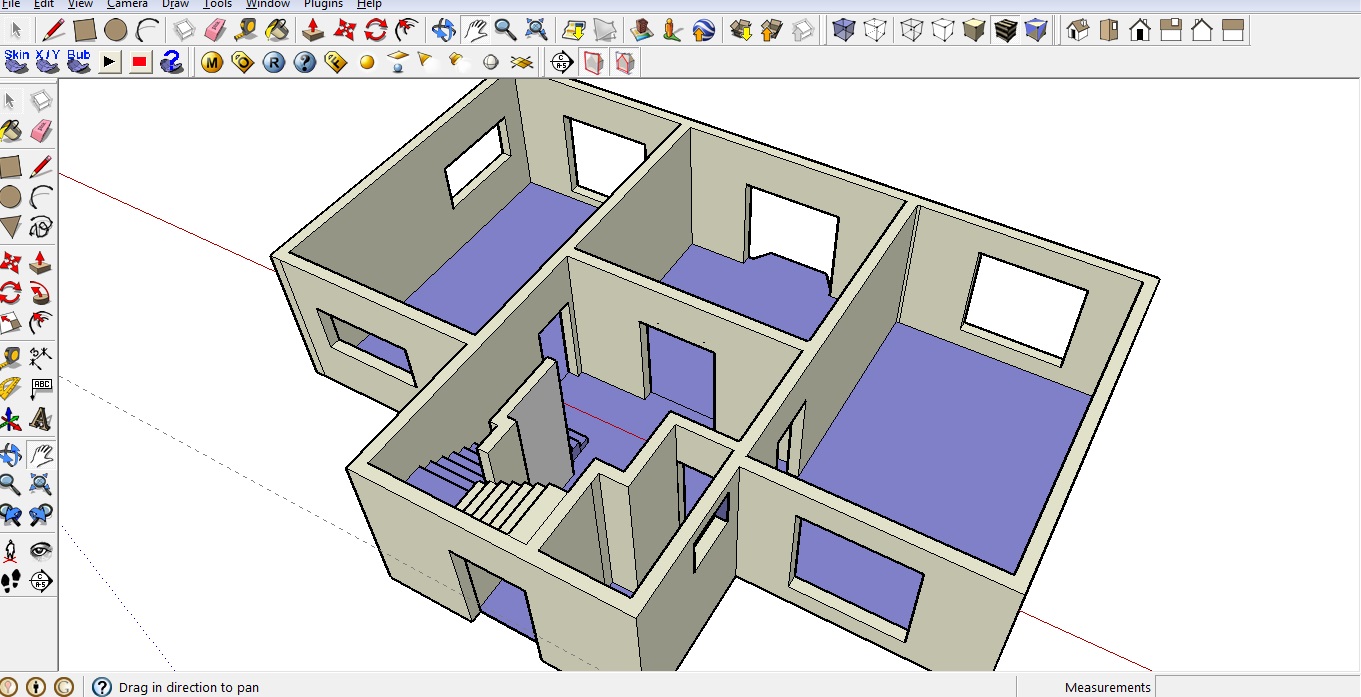

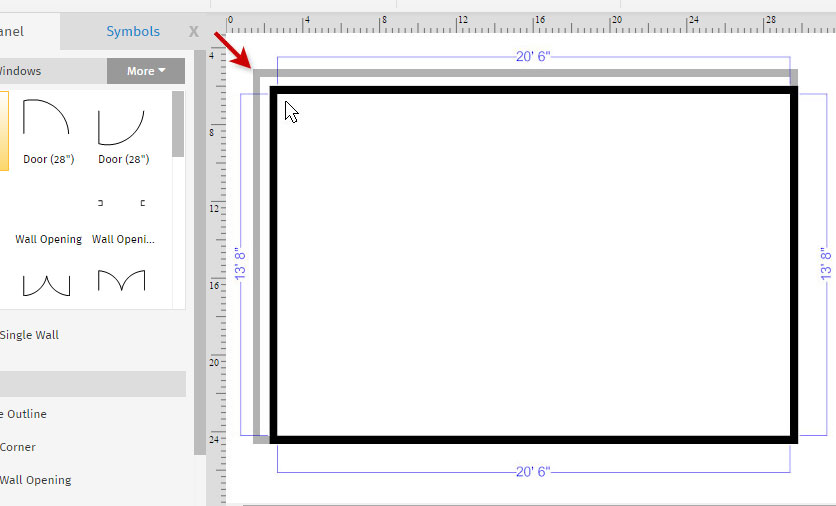

(You can also do this by going to the Virtuoso Options You can fix this by hitting Shift-F to display all levels Now, you will notice that you don't immediately see what is inside the Finally, hit "Escape" to stop adding instances. Place the two NMOS and two PMOS transistors so that your layout looks Release the button, you should see that the instance is much larger. Right-click and drag a box around the origin. You may want to zoom in before placing the instance. Instance at the tip of your cursor, as shown below. Next, move the cursor into the layout editor window. The same value as in you schematics (e.g., 540nm). Then scroll down in the create-instanceĭialog to look for a parameter called Width. Select the library "NCSU_TechLib_tsmc02d", cell "nmos", view "layout". Next, click "Browse" on the screen that appears and TheseĬells are parameterized cells (or p-cells) which change theirįeatures when you change their parameters.Ĭreate->Instance, or simply hit "i". You learn to place copies of other cells: pmos and nmos. Now you are ready to draw objects in the Virtuoso window. Other than that, the process of wiring up the cell is pretty much the same Also the pins for vdd, gnd, A and B have already been created. What should be connected to what, based on the connectivity in the That when you move the cells orange "flylines" will appear telling you Now you need to move the cells into position and wire them up. Transistors/sizes and pins already put down for you: The layout should now look like this with all the correct The defaults should be set for you, as below:

#Layouteditor drawing verification

This is not essential since we always verify that the layout isĬorrect using the LVS verification path as well.Ĭonnectivity->Generate->All from Source The following popup appears.

The layout for you, and it maintains connectivity information between the

That means it can directly generate the basic components into Maintain the "layout vs schematic" (LVS) information from the beginning of The primary difference between Virtuoso L and XL is that XL attempts to InĮither case you must first perform the mapping of logical to physical cells. XL find the cells in the schematic and put them in the layout for you. Transistor "P-Cells" into your schematic "by hand", or you can let Virtuoso You can create (drag and drop) instances of Once you have done that correctly, the line for that device will turn Then double left click under Physical Cell to select nmos (or pmos) Library" This will bring up a scroll menu for you to select NCSU_tsmc02d Double Left Click on the pink area under the words "Physical Now you must set the physical library and physical cell name for each Therefore the transistors need to be mapped. Transistors for layout and the logical names used in the schematic do not

In addition, the LSW window (Layer Selection Window), which shows variousįor the CDK 1.6 beta TSMC02d library the physical names of the To build your layout at the origin to simplify the use of the cell by place Layout window does have and use coordinates for physical positions.

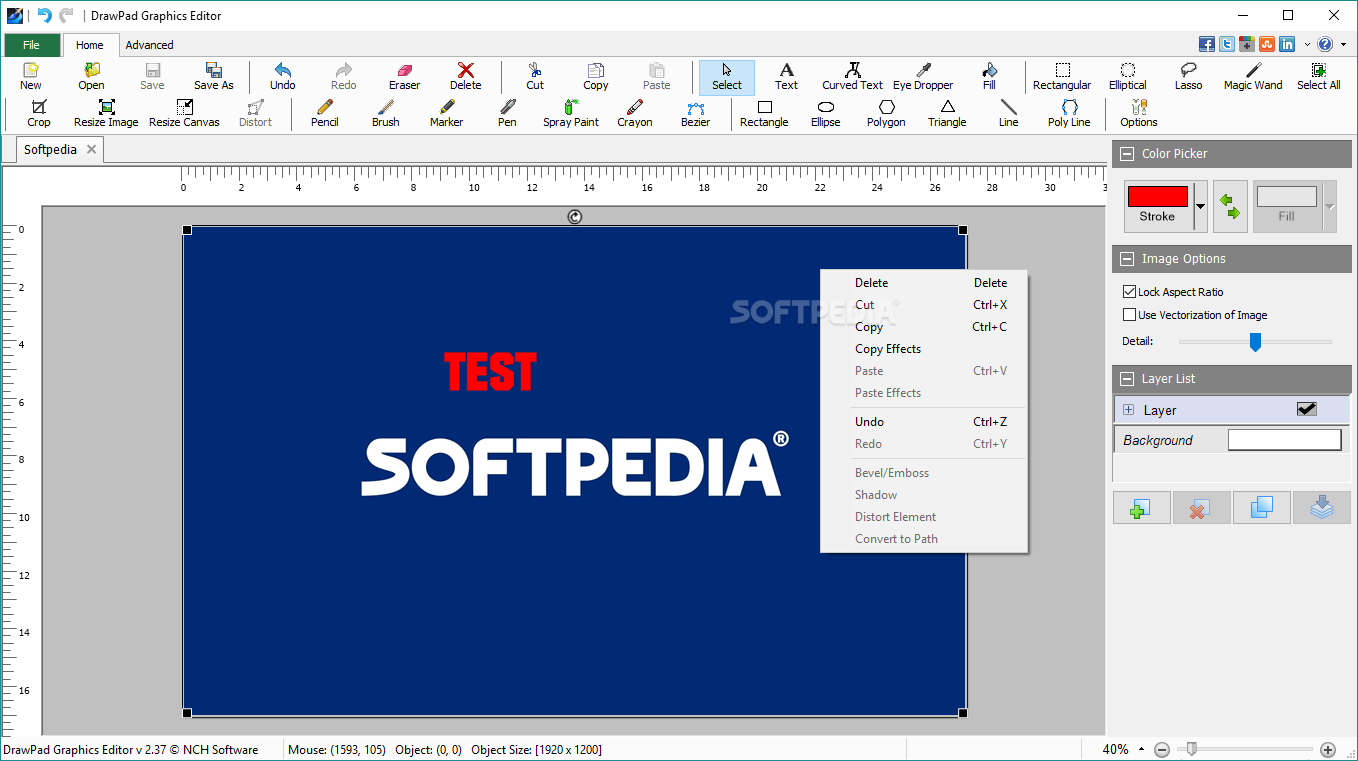

#Layouteditor drawing windows

This will open two windows The first is the schematic window you justĬlosed, and the second is the layout window below Note that the "Application" is automatically set to "Layout Simply NAND2 should be filled in for cell-name and change the Next, select the NAND2 cell the Library Manager and select File->New->Cell View. This window allows you to browse the available libraries and create your own. Open the library manager by selecting Tools->LibraryManager. Once you are happy with your simulation, close the ADE.Gate schematic (called NAND2 in the library Lab1) Use virtuoso to create and simulate a 2 input NAND.Start the Cadence Design Framework (virtuoso).Tutorial on setting up the design environment and running Virtuoso

0 kommentar(er)

0 kommentar(er)